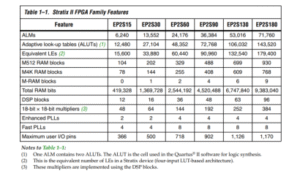

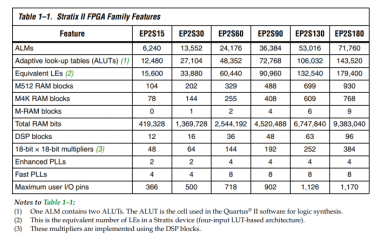

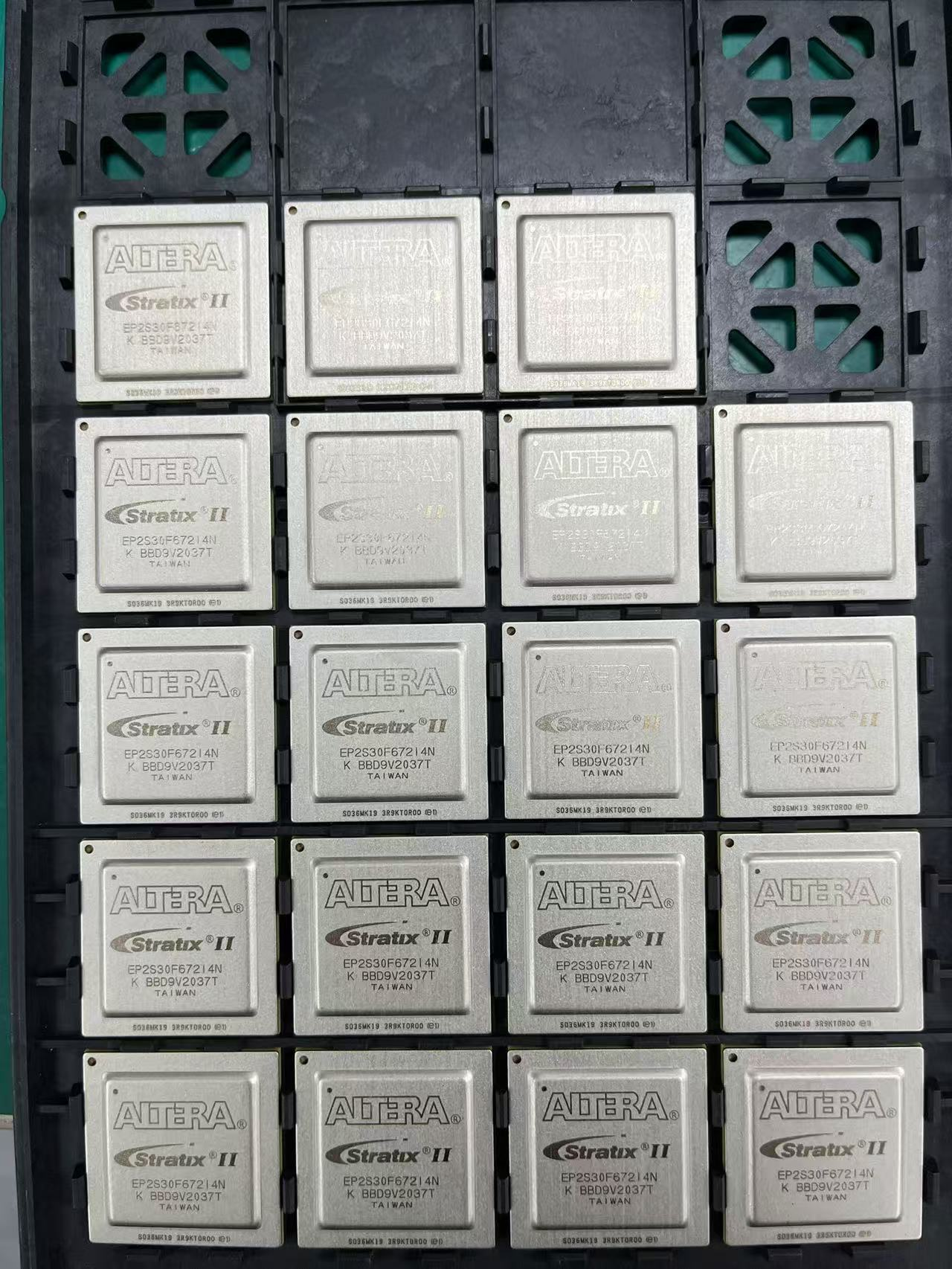

The Stratix® Il FPGA family is based on a 1.2-V, 90-nm, all-layer copperSRAM process and features a new logic structure that maximizesperformance, and enables device densities approaching 180,000equivalent logic elements (LEs). Stratix I devices offer up to 9 Mbits ofon-chip, TriMatrixTm memory for demanding, memory intensiveapplications and has up to 96 DSP blocks with up to 384 (18-bit x 18-bit)multipliers for efficient implementation of high performance filters andother DSP functions. Various high-speed external memory interfaces aresupported, including double data rate (DDR) SDRAM and DDR2SDRAM, RLDRAM Il, quad data rate (ODR) I SRAM, and single datarate (SDR) SDRAM. Stratix I devices support various I/O standardsalong with support for 1-gigabit per second (Gbps) source synchronoussignaling with DPA circuitry, Stratix I devices offer a complete clockmanagement solution with internal clock frequency of up to 550 MHzand up to 12 phase-locked loops (PLLs). Stratix I devices are also theindustry’s first FPGAs with the ability to decrypt a configurationbitstream using the Advanced Encryption Standard (AES) algorithm toprotect designs.

评价

目前还没有评价